3

4

5

**Document Identifier: DSP0233**

Date: 2024-03-25

Version: 1.0.1

# Management Component Transport Protocol (MCTP) I3C Transport Binding Specification

8 Supersedes: 1.0.0

9 **Document Class: Normative**

10 Document Status: Published

11 Document Language: en-US

- 12 Copyright Notice

- 13 Copyright © 2021, 2024 DMTF. All rights reserved.

- 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems

- 15 management and interoperability. Members and non-members may reproduce DMTF specifications and

- 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to

- 17 time, the particular version and release date should always be noted.

- 18 Implementation of certain elements of this standard or proposed standard may be subject to third-party

- 19 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations

- to users of the standard as to the existence of such rights and is not responsible to recognize, disclose, or

- 21 identify any or all such third-party patent right owners or claimants, nor for any incomplete or inaccurate

- 22 identification or disclosure of such rights, owners, or claimants. DMTF shall have no liability to any party,

- in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, disclose, or

- 24 identify any such third-party patent rights, or for such party's reliance on the standard or incorporation

- 25 thereof in its products, protocols, or testing procedures. DMTF shall have no liability to any party

- implementing such standards, whether such implementation is foreseeable or not, nor to any patent

- owner or claimant, and shall have no liability or responsibility for costs or losses incurred if a standard is

- 28 withdrawn or modified after publication, and shall be indemnified and held harmless by any party

- 29 implementing the standard from any and all claims of infringement by a patent owner for such

- 30 implementations.

- 31 For information about patents held by third-parties which have notified DMTF that, in their opinion, such

- 32 patents may relate to or impact implementations of DMTF standards, visit

- 33 https://www.dmtf.org/about/policies/disclosures.

- 34 PCI-SIG, PCIe, and the PCI HOT PLUG design mark are registered trademarks or service marks of PCI-

- 35 SIG. I3C is a registered service mark of MIPI Alliance, Inc.

- 36 All other marks and brands are the property of their respective owners.

- 37 This document's normative language is English. Translation into other languages is permitted.

38 CONTENTS

| 39       | Foreword5                                                                       |                         |                                                       |    |  |  |

|----------|---------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------|----|--|--|

| 40       | Introduction                                                                    |                         |                                                       |    |  |  |

| 41       | 1                                                                               | Scope                   |                                                       |    |  |  |

| 42       | 2                                                                               | Normative references    |                                                       |    |  |  |

| 43       | 3                                                                               | Terms and definitions   |                                                       |    |  |  |

| 44       | 4                                                                               |                         |                                                       |    |  |  |

| 45       | •                                                                               |                         | nassigned values                                      |    |  |  |

| 46       |                                                                                 |                         |                                                       |    |  |  |

| 47       | 5                                                                               | -                       | ort                                                   |    |  |  |

| 48       | -                                                                               |                         | I3C                                                   |    |  |  |

| 49       |                                                                                 | 5.1.1 I3C bus           | physical topology                                     | 12 |  |  |

| 50       |                                                                                 | 5.1.2 I3C com           | nmunication logical topology and MCTP packet bridging | 13 |  |  |

| 51       |                                                                                 |                         | Bus Owner for I3C bus                                 |    |  |  |

| 52       |                                                                                 | 5.2 MCTP packet er      | ncapsulation                                          | 15 |  |  |

| 53       |                                                                                 |                         | packet encapsulation: I3C Controller to I3C Target    |    |  |  |

| 54       |                                                                                 |                         | packet encapsulation: I3C Target to I3C Controller    |    |  |  |

| 55<br>56 |                                                                                 |                         | and handling mechanisms                               |    |  |  |

| 56<br>57 |                                                                                 |                         | lata packetsror detection and handling                |    |  |  |

| 58       |                                                                                 |                         | SDA" condition handling                               |    |  |  |

| 59       |                                                                                 |                         | and capabilities discovery                            |    |  |  |

| 60       |                                                                                 | - 11                    | tion and discovery flow                               |    |  |  |

| 61       |                                                                                 |                         | ission unit sizes                                     |    |  |  |

| 62       |                                                                                 |                         | a                                                     |    |  |  |

| 63       |                                                                                 |                         | s format for MCTP control messages                    |    |  |  |

| 64       |                                                                                 |                         | medium-specific information                           |    |  |  |

| 65       |                                                                                 |                         | nd control message timing requirements                |    |  |  |

| 66       |                                                                                 |                         | tation                                                |    |  |  |

| 67       | ANN                                                                             | EX B (informative) Ch   | ange log                                              | 33 |  |  |

| 68       |                                                                                 |                         |                                                       |    |  |  |

| 69       | Fig                                                                             | ures                    |                                                       |    |  |  |

| 70       | Figu                                                                            | re 1 – Physical topolog | y of I3C bus                                          | 13 |  |  |

| 71       |                                                                                 |                         | of MCTP over I3C communication                        |    |  |  |

| 72       | -                                                                               |                         | get as MCTP Bus Owner & bridge                        |    |  |  |

| 73       | Figure 4 – MCTP over I3C packet transfer format: I3C Controller to I3C Target   |                         |                                                       |    |  |  |

| 74       | Figure 5 – MCTP over I3C packet transfer sequence: I3C Target to I3C Controller |                         |                                                       |    |  |  |

| 75       | Figure 6 – MCTP over I3C packet transfer format: I3C Target to I3C Controller   |                         |                                                       |    |  |  |

| 76       | Figure 7 – Sample I3C dynamic address assignment flow and MCTP discovery        |                         |                                                       |    |  |  |

|          | rigu                                                                            |                         | arnic address assignment now and MCTF discovery       | ∠€ |  |  |

| 77       |                                                                                 |                         |                                                       |    |  |  |

### Tables

78

| 79 | Table 1 – MCTP packet transfer field descriptions                | 16 |

|----|------------------------------------------------------------------|----|

| 80 | Table 2 – IBI pending read notification field descriptions       | 19 |

| 81 | Table 3 – MCTP packet transfer field descriptions                | 20 |

| 82 | Table 4 – Recommended behaviors for robust CCCs                  | 23 |

| 83 | Table 5 – Physical address format                                | 28 |

| 84 | Table 6 – Medium-specific information                            | 29 |

| 85 | Table 7 – Timing specifications for MCTP data packets on I3C     | 29 |

| 86 | Table 8 – Timing specifications for MCTP control messages on I3C | 30 |

| 87 |                                                                  |    |

| 88                                                                          | Foreword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 89<br>90<br>91                                                              | The Management Component Transport Protocol (MCTP) I3C Transport Binding Specification (DSP0233 was prepared by the DMTF PMCI Working Group in close cooperation with the MIPI Alliance I3C Working Group.                                                                                                                                                                                                                                                                                                          |

| 92<br>93                                                                    | DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability.                                                                                                                                                                                                                                                                                                                                                                             |

| 94<br>95<br>96<br>97                                                        | MIPI Alliance is a collaborative global organization serving industries that develop mobile and mobile-influenced devices. The focus of the organization is to design and promote hardware and software interfaces that simplify the integration of components built into a device, from the antenna and modem to peripherals and the application processor.                                                                                                                                                        |

| 98                                                                          | This version supersedes version 1.0.0. For a list of changes, see the change log in ANNEX B.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 99                                                                          | Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 100                                                                         | DMTF acknowledges the following individuals for their contributions to this document:                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 101                                                                         | Editors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 102<br>103<br>104                                                           | <ul> <li>Janusz Jurski – Intel Corporation</li> <li>Myron Loewen – Solidigm</li> <li>Amit K. Srivastava – Intel Corporation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              |

| 105                                                                         | DMTF Contributors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 106<br>107<br>108<br>109<br>110<br>111<br>112<br>113<br>114<br>115          | <ul> <li>Patrick Caporale – Lenovo</li> <li>Yuval Itkin – NVIDIA Corporation</li> <li>John Leung – Intel Corporation</li> <li>Eliel Louzoun – Intel Corporation</li> <li>Balaji Natrajan – Microchip Technology Inc.</li> <li>Edward Newman – Hewlett Packard Enterprise</li> <li>Jim Panian – Qualcomm Incorporated</li> <li>William Scherer III – Hewlett Packard Enterprise</li> <li>Hemal Shah – Broadcom Inc</li> <li>Bob Stevens – Dell Inc.</li> <li>Johan Van De Groenendaal – Intel Corporation</li> </ul> |

| 17                                                                          | MIPI Contributors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 118<br>  19<br>  20<br>  21<br>  22<br>  23<br>  24<br>  25<br>  26<br>  27 | <ul> <li>Guruprasad Ardhanari – Intel Corporation</li> <li>Jerry Backer – Intel Corporation</li> <li>Rajesh Bhaskar – Intel Corporation</li> <li>Enrico D. Carrieri – Intel Corporation</li> <li>Anamitra Chakrabarti – Synopsys, Inc.</li> <li>Kelly J. Couch – Intel Corporation</li> <li>Kenneth P. Foust – Intel Corporation</li> <li>Chris Grigg – MIPI Alliance (Team)</li> <li>David Harriman – Intel Corporation</li> <li>Prakash Iyer – Intel Corporation</li> </ul>                                       |

| 28                                                                          | Paul Kimelman – NXP Semiconductors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 129                                                                         | <ul> <li>Łukasz Łanecki – Intel Corporation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### **MCTP I3C Transport Binding Specification**

**DSP0233**

| • | Richard Marian Thomaiyar – Intel Corporation |

|---|----------------------------------------------|

| • | Tim E. McKee – Intel Corporation             |

| • | Mariusz Oriol – Intel Corporation            |

| • | Ankit Rohatgi – MIPI Alliance (Team)         |

| • | Matthew Schnoor – Intel Corporation          |

| • | Eyuel Zewdu Teferi – STMicroelectronics      |

| • | George Vergis – Intel Corporation            |

|   | •                                            |

### DSP0233

### **MCTP I3C Transport Binding Specification**

| 137                     | Introduction                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 138<br>139<br>140       | The Management Component Transport Protocol (MCTP) over I3C transport binding defines a transport binding for facilitating communication between platform management subsystem components (e.g., management controllers, managed devices) over I3C.                                                                                                                                       |  |  |

| 41<br> 42<br> 43<br> 44 | The <u>Management Component Transport Protocol (MCTP) Base Specification</u> describes the protocol and commands used for communication within and initialization of an MCTP network. The MCTP over I3C transport binding definition in this specification includes a packet format, physical address format, message routing, and discovery mechanisms for MCTP over I3C communications. |  |  |

### 145 **1 Scope**

148

- 146 This document provides the specifications for the Management Component Transport Protocol (MCTP)

- 147 transport binding for I3C.

### 2 Normative references

- The following referenced documents are indispensable for the application of this document. For dated or

- versioned references, only the edition cited (including any corrigenda or DMTF update versions) applies.

- 151 For references without a date or version, the latest published edition of the referenced document

- 152 (including any corrigenda or DMTF update versions) applies.

- 153 DMTF, DSP0236, Management Component Transport Protocol (MCTP) Base Specification 1.3,

- https://www.dmtf.org/dsp/DSP0236

- 155 DMTF, DSP0239, Management Component Transport Protocol (MCTP) IDs and Codes 1.8,

- 156 <a href="https://www.dmtf.org/dsp/DSP0239">https://www.dmtf.org/dsp/DSP0239</a>

- 157 ISO/IEC Directives, Part 2, Principles and rules for the structure and drafting of ISO and IEC documents,

- 158 https://www.iso.org/sites/directives/current/part2/index.xhtml

- 159 Specification for I3C Basic<sup>SM</sup>, Improved Inter Integrated Circuit Basic, Version 1.0,

- 160 <u>https://www.mipi.org/specifications/i3c-sensor-specification</u>

- Note: this specification relies on version 1.0 of the referenced document, but implementers are

- 162 encouraged to follow the latest published version.

- 163 MIPI Mandatory Data Byte (MDB) Values Table,

- 164 https://www.mipi.org/MIPI I3C mandatory data byte values public

- 165 MIPI Device Characteristics Register (DCR) Assignments,

- 166 https://www.mipi.org/MIPI I3C device characteristics register

- 167 MIPI I3C SM Host Controller Interface SM v1.0 Specification, MIPI, April 2018,

- 168 <a href="https://www.mipi.org/specifications/i3c-hci">https://www.mipi.org/specifications/i3c-hci</a>

- Note: this specification relies on version 1.0 of the referenced document but implementers are

- 170 encouraged to follow the latest published version

- 171 System Management Bus (SMBus) Specification v2.0, SBS Implementers Forum, SMBus, August 2000,

- 172 http://www.smbus.org/specs/smbus20.pdf

- Note: this specification relies on version 2.0 of the referenced document, but implementers are

- 174 encouraged to follow the latest published version.

### 3 Terms and definitions

- 176 In this document, some terms have a specific meaning beyond the normal English meaning. Those terms

- 177 are defined in this clause.

175

- 178 The terms "shall" ("required"), "shall not", "should" ("recommended"), "should not" ("not recommended"),

- "may", "need not" ("not required"), "can" and "cannot" in this document are to be interpreted as described

- in ISO/IEC Directives, Part 2, Clause 7. The terms in parentheses are alternatives for the preceding term,

- for use in exceptional cases when the preceding term cannot be used for linguistic reasons. Note that

- 182 ISO/IEC Directives, Part 2, Clause 7 specifies additional alternatives. Occurrences of such additional

- alternatives shall be interpreted in their normal English meaning.

- The terms "clause", "subclause", "paragraph", and "annex" in this document are to be interpreted as

- described in ISO/IEC Directives, Part 2, Clause 6.

#### **DSP0233**

- 186 The terms "normative" and "informative" in this document are to be interpreted as described in ISO/IEC

- 187 Directives, Part 2, Clause 3. In this document, clauses, subclauses, or annexes labeled "(informative)" do

- 188 not contain normative content. Notes and examples are always informative elements.

- 189 Refer to Management Component Transport Protocol (MCTP) Base Specification for the terms and

- definitions that are used across the MCTP specifications.

- For the purposes of this document, the following terms and definitions apply.

- 192 **3.1**

- 193 Address Resolution Protocol

- 194 **ARP**

- 195 refers to the procedure used to dynamically determine the addresses of devices on a shared

- 196 communication medium

- 197 **3.2**

- 198 **ACK**

- 199 Acknowledge

- 200 3.3

- 201 BCR

- 202 Bus Characteristics Register see Specification for I3C Basic<sup>SM</sup>, Improved Inter Integrated Circuit Basic

- 203 for more information

- 204 **3.4**

- 205 **BMC**

- 206 Baseboard management controller

- 207 3.5

- 208 CCC

- 209 Common Command Code see Specification for I3C Basic<sup>SM</sup>, Improved Inter Integrated Circuit Basic

- 210 for more information

- 211 **3.6**

- 212 **Destination Device**

- 213 Device receiving the MCTP packet over I3C bus

- 214 **3.7**

- 215 **EEPROM**

- 216 Electrically Erasable Programmable Read-Only Memory

- 217 **3.8**

- 218 **EID**

- 219 Endpoint identifier

- **220 3.9**

- 221 **HCI**

- 222 Host Controller Interface

- 223 **3.10**

- 224 Hot-Join

- Joining the Bus after it is already started see Specification for I3C Basic<sup>SM</sup>, Improved Inter Integrated

- 226 <u>Circuit Basic</u> for more information

- 227 **3.11**

- 228 **I3C**

- 229 Improved Inter-Integrated Circuit see Specification for I3C Basic<sup>SM</sup>, Improved Inter Integrated Circuit –

- 230 Basic for more information

- 231 **3.12**

- 232 I3C Master / I3C Controller / Primary

- 233 The "I3C Master" and "I3C Controller" terms are equivalent the original revision of Specification for I3C

- 234 Basic<sup>SM</sup>, Improved Inter Integrated Circuit Basic defined the "I3C Master" term while the updated MIPI

- specification revisions used the "I3C Controller" term; the initial revision of this specification sometimes

- also used the term "Primary" when referring to the "I3C Controller" or "I3C Master"

- 237 **3.13**

- 238 I3C Slave / I3C Target / Secondary

- 239 The "I3C Slave" and "I3C Target" terms are equivalent the original revision of Specification for I3C

- 240 Basic<sup>SM</sup>, Improved Inter Integrated Circuit Basic defined the "I3C Slave" term while the updated MIPI

- 241 specification revisions used the "I3C Target" term; the initial revision of this specification sometimes also

- used the term "Secondary" when referring to the "I3C Target" or "I3C Slave"

- 243 **3.14**

- 244 **IBI**

- 245 In-Band Interrupt see Specification for I3C Basic<sup>SM</sup>, Improved Inter Integrated Circuit Basic for more

- 246 information

- 247 **3.15**

- 248 max

- 249 maximum

- 250 **3.16**

- 251 **MCTP**

- 252 Management Component Transport Protocol

- 253 **3.17**

- 254 **MDB**

- 255 Mandatory Data Byte

- 256 **3.18**

- 257 **MHz**

- 258 megahertz

- 259 **3.19**

- 260 min

- 261 minimum

- 262 **3.20**

- 263 **ms**

- 264 millisecond

- 265 **3.21**

- 266 **MSB**

- 267 most significant byte

#### **DSP0233**

- 268 **3.22**

- 269 **MTU**

- 270 Maximum Transmission Unit

- **271 3.23**

- 272 **NACK**

- 273 not acknowledge

- 274 **3.24**

- 275 **PC**

- 276 peripheral component interconnect

- **277 3.25**

- 278 **PCle**®

- 279 PCI Express™

- 280 **3.26**

- 281 **PEC**

- 282 packet error code

- 283 **3.27**

- 284 **PMCI**

- 285 Platform Management Component Intercommunications

- 286 **3.28**

- 287 SCL

- 288 serial clock

- 289 **3.29**

- 290 SDA

- 291 serial data

- 292 3.30

- 293 **sec**

- 294 second

- **295 3.31**

- 296 **SMBus**

- 297 System Management Bus

- 298 **3.32**

- 299 Source Device

- 300 Device sending the MCTP packet over I3C bus

- **301 3.33**

- 302 **T-bit**

- 303 Transition bit see <u>Specification for I3C Basic SM</u>, <u>Improved Inter Integrated Circuit Basic</u> for more

- 304 information

- 305 3.34

- 306 **UDID**

- 307 unique device identifier

### 308 4 Conventions

310

The conventions described in the following clauses apply to this specification.

### 4.1 Reserved and unassigned values

- 311 Unless otherwise specified, any reserved, unspecified, or unassigned values in enumerations or other

- 312 numeric ranges are reserved for future definition by DMTF.

- Unless otherwise specified, numeric or bit fields that are designated as reserved shall be written as 0

- 314 (zero) and ignored when read.

### 315 **4.2 Byte ordering**

- 316 Unless otherwise specified, byte ordering of multi-byte numeric fields or bit fields is "Big Endian" (that is,

- 317 the lower byte offset holds the most significant byte, and higher offsets hold lesser significant bytes).

### 318 5 MCTP over I3C transport

- 319 The MCTP over I3C transport binding defines how MCTP packets are delivered over a physical I3C

- 320 medium using I3C transfers. See <u>Specification for I3C Basic<sup>SM</sup></u>, <u>Improved Inter Integrated Circuit Basic</u>

- 321 for complete details about I3C requirements, including the electrical layer. This specification defines

- 322 additional requirements and supersedes the <u>Specification for I3C Basic<sup>SM</sup></u>, <u>Improved Inter Integrated</u>

- 323 <u>Circuit Basic</u> in any cases when there are differences.

- 324 This binding specification has been designed to be able to share the same bus with devices

- 325 communicating using other I3C protocols (e.g., MIPI Debug for I3C<sup>SM</sup> see clause 5.4.1) and compatible

- 326 SMBus/I2C devices (e.g., EEPROM). Interactions with such devices or protocols are out of scope for this

- 327 specification.

329

### 328 5.1 MCTP use with I3C

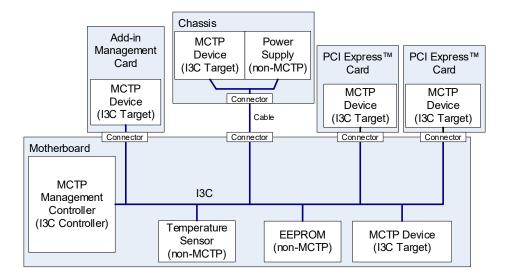

### 5.1.1 I3C bus physical topology

- 330 The physical topology of the I3C bus is presented in Figure 1. There is a single device that plays the role

- of the I3C Controller (typically it is a Management Controller, Embedded Controller, etc.) and there may

- be multiple I3C Targets sharing the same I3C bus. Specification for I3C Basic<sup>SM</sup>, Improved Inter

- 333 Integrated Circuit Basic defines the Secondary Controller but that is not required for implementing

- 334 MCTP and is out of scope for this specification.

336

Figure 1 - Physical topology of I3C bus

337

338

339

340

341

342 343

### 5.1.2 I3C communication logical topology and MCTP packet bridging

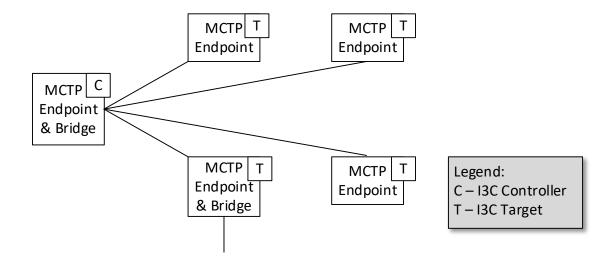

The topology of the logical communication paths is shown in Figure 2. The I3C Controller can communicate to any of the I3C Targets. Each I3C Target can communicate with the I3C Controller only. Any communications between I3C Targets are implemented by MCTP bridge functionality in the I3C Controller, according to the *Management Component Transport Protocol (MCTP) Base Specification*. Unlike typical MCTP bridges that transfer data to another port, this data may be retransmitted to the same

port. When forwarding, the physical addressing and PEC gets changed by the bridge to match the requirements of the destination bus.

Figure 2 – Logical topology of MCTP over I3C communication

Note that the <u>Specification for I3C Basic<sup>SM</sup></u>, <u>Improved Inter Integrated Circuit – Basic</u> has its own concept of an I3C bridge device and it requires that I3C bridges implement certain functionality and report their capability using BCR[4] flag. MCTP bridges are a different concept from I3C bridges.

There is no relationship between the physical layer I3C addresses and the transport protocol layer MCTP EIDs. I3C addresses are assigned by the I3C Controller, while MCTP EIDs are assigned by the MCTP Bus Owner. These two functions are logically independent but they may be collocated.

### 5.1.3 MCTP Bus Owner for I3C bus<sup>1</sup>

As defined in <u>Management Component Transport Protocol (MCTP)</u> Base Specification, MCTP Bus Owner device is responsible for MCTP endpoints discovery and managing MCTP EID assignments. EID assignment requires physical addressing to be used (with EID = 0, i.e., Null Destination EID or Null Source EID). On the I3C bus, direct communication can only happen with the I3C Controller either as a source or a destination, as described in the previous clause.

There may be multiple logical MCTP buses overlaid on a single I3C physical bus:

- Preferably, the I3C Controller is the MCTP Bus Owner. It can discover all the I3C Targets and fulfil the MCTP Bus Owner role for the whole I3C bus (see clause 5.4.1 for the flow details).

- Additionally, an I3C Target can be an MCTP Bus Owner but only for the connection between it

and the I3C Controller (see clause 5.4.1 for the flow details as well). Other I3C Target devices on

the I3C bus are not directly reachable by the I3C Target. I3C Target acting as an MCTP Bus

Owner enables it to act as an MCTP bridge from another MCTP bus. An I3C Target that acts as

an MCTP Bus Owner cannot be added to an I3C bus using the I3C hot-join mechanism.

.

<sup>&</sup>lt;sup>1</sup> The term "bus" is used in a different meaning in <u>Specification for I3C Basic<sup>SM</sup>, Improved Inter Integrated Circuit – Basic</u> and in <u>Management Component Transport Protocol (MCTP) Base Specification</u> context. This clause describes a scenario when multiple MCTP buses are overlaid on a single I3C bus.

370 371

372 373

374

375

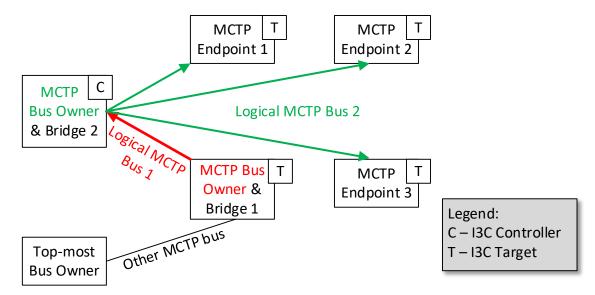

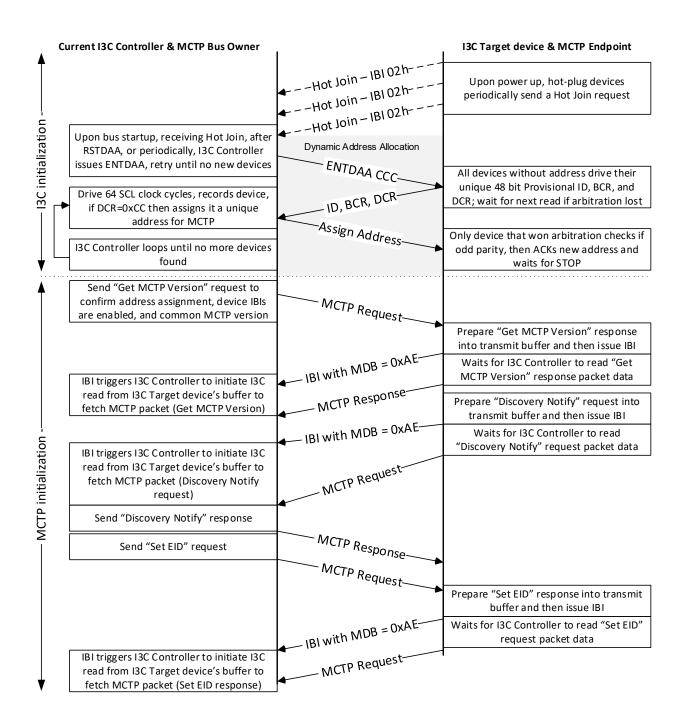

368 For example, as shown in Figure 3, two logical buses are created and EIDs are assigned as follows:

- Logical MCTP Bus 1, Bridge 1 (I3C Target) is the MCTP Bus Owner Bridge 1 assigns the EID and EID pool to the I3C Controller because I3C Controller is an endpoint on the Logical MCTP Bus 1.

- Logical MCTP Bus 2, Bridge 2 (I3C Controller) is the MCTP Bus Owner for Logical MCTP Bus 2 Bridge 2 assigns EIDs to all the remaining I3C Targets.

This concept can be extended and each device on an I3C bus could be a MCTP Bridge to additional MCTP networks.

Figure 3 - Sample I3C Target as MCTP Bus Owner & bridge

378

379

380

381

382

385

386

387

388

389

390 391

376

377

### 5.2 MCTP packet encapsulation

MCTP packet transfers over I3C slightly differ depending on the communication direction:

- I3C Controller to I3C Target communication follows encapsulation defined in clause 5.2.1

- I3C Target to I3C Controller communication follows encapsulation defined in clause 5.2.2

Subclauses below capture the MCTP packet encapsulation details. There is no requirement for the multipacket MCTP message to be contiguous on the bus.

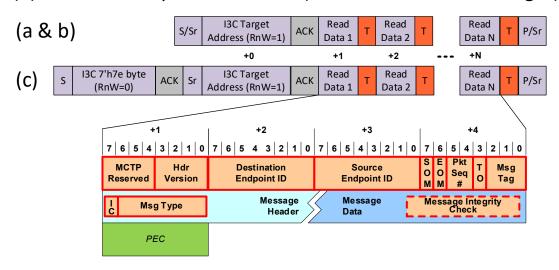

### 5.2.1 MCTP packet encapsulation: I3C Controller to I3C Target

### **5.2.1.1** Overview

Transmission of MCTP packets from the I3C Controller to the I3C Target happens using private write transfer initiated by I3C Controller as defined in <u>Specification for I3C Basic<sup>SM</sup></u>, <u>Improved Inter Integrated Circuit – Basic</u>. The transfer shall be directed to the I3C Target address used for MCTP protocol communication. For the purpose of this specification, an I3C Target shall only support the MCTP protocol at its unique I3C Target address and an I3C address shall be dynamically assigned for that

Version 1.0.1 Published 15

purpose. See clause 5.4.1 for discussion about protocol discovery when other protocols may be in use on the I3C bus.

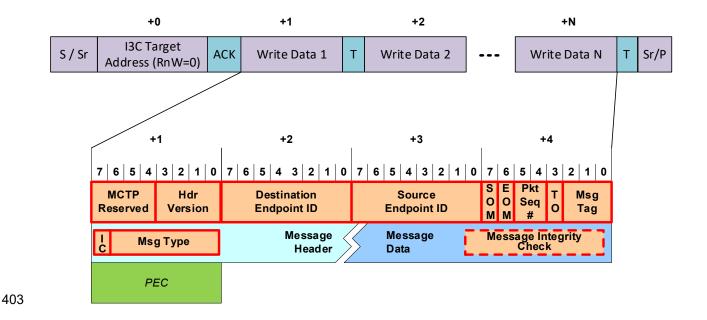

The MCTP message header and MCTP message data fields map to I3C payload as indicated in Figure 4. After the MCTP message data, there is a PEC byte added – its role is discussed in clause 5.3.1. Please note that the length of the write transfer is dictated by the I3C Controller using Repeated Start/Stop condition. I3C Controller is expected to obey the discovered maximum write length (see clause 5.4.2 for more information).

Note that the I3C Target does not need I3C address of the I3C Controller because all MCTP packets from a given I3C Target will always be directed to the I3C Controller – the I3C Controller has no explicit address as per <u>Specification for I3C Basic<sup>SM</sup></u>, <u>Improved Inter Integrated Circuit – Basic</u>. MCTP Destination EID should be used to route the MCTP packet to another I3C Target if necessary.

Figure 4 – MCTP over I3C packet transfer format: I3C Controller to I3C Target

Please note that the MCTP packet transfer shown may be preceded by the optional I3C Broadcast Address (7'h7E), as defined in the I3C specification. In this transaction, the T-bit is the parity of each byte.

As per the <u>Management Component Transport Protocol (MCTP) Base Specification</u>, IC and Message Type byte is only present in the first packet of a fragmented MCTP message.

Table 1 - MCTP packet transfer field descriptions

| Byte | I3C Field(s)       | Description                                                                          |

|------|--------------------|--------------------------------------------------------------------------------------|

| 0    | I3C Target Address | [7:1] I3C Target Address: The address of the I3C Target on the local I3C bus         |

|      | KIIVV              | [0] I3C RnW# bit: Shall be set to 0b as all MCTP messages using I3C write transfers. |

16 Published Version 1.0.1

| Byte       | I3C Field(s)                                                                                                            | Description                                                                                                                                                                                             |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | Write Data 1                                                                                                            | [7:4] MCTP reserved: This nibble is reserved for definition by the<br><u>Management Component Transport Protocol (MCTP) Base</u><br><u>Specification</u> .                                              |  |  |

|            |                                                                                                                         | [3:0] MCTP header version:                                                                                                                                                                              |  |  |

|            |                                                                                                                         | Set to 0001b for MCTP v1 devices that are conformant to the<br><u>Management Component Transport Protocol (MCTP) Base</u><br><u>Specification</u> and this version of the MCTP transport binding.       |  |  |

|            |                                                                                                                         | All other values = Reserved.                                                                                                                                                                            |  |  |

| 2          | Write Data 2                                                                                                            | Destination Endpoint ID (*) as defined in <u>Management Component</u> <u>Transport Protocol (MCTP) Base Specification</u> , including special endpoint IDs                                              |  |  |

| 3          | Write Data 3                                                                                                            | Source Endpoint ID (*) as defined in <u>Management Component Transport Protocol (MCTP) Base Specification</u> , including special endpoint IDs                                                          |  |  |

| 4          | Write Data 4                                                                                                            | [7] SOM: Start Of Message flag (*)                                                                                                                                                                      |  |  |

|            |                                                                                                                         | [6] EOM: End Of Message flag (*)                                                                                                                                                                        |  |  |

|            |                                                                                                                         | [5:4] MCTP Packet sequence number (*)                                                                                                                                                                   |  |  |

|            |                                                                                                                         | [3] Tag Owner (TO) bit (*)                                                                                                                                                                              |  |  |

| _          |                                                                                                                         | [2:0] Message tag (*)                                                                                                                                                                                   |  |  |

| 5          | Write Data 5                                                                                                            | [7] IC: Integrity Check bit (*)                                                                                                                                                                         |  |  |

|            |                                                                                                                         | [6:0] Message type (*)                                                                                                                                                                                  |  |  |

| 6:N-1      | Write Data 6:N-1                                                                                                        | MCTP message header and data (*)                                                                                                                                                                        |  |  |

| N          | PEC                                                                                                                     | Packet error code (PEC): All MCTP I3C transfers shall include a PEC byte. The PEC byte shall be transmitted by the source and checked by the destination. Please see clause 5.3.1 for more information. |  |  |

| (*) Indica | (*) Indicates a field that is defined by the <u>Management Component Transport Protocol (MCTP) Base Specification</u> . |                                                                                                                                                                                                         |  |  |

### 5.2.1.2 I3C Target address ACKs/NACKs

- The I3C Controller can start another write transfer after the Repeated Start condition on the bus, meaning

- 412 that multiple MCTP packets can follow one after the other in sequence. In case the I3C Target buffer

- 413 cannot accommodate the maximum packet length (as negotiated according to clause 5.4.2), it shall

- NACK its address to indicate the potential overflow and a need for retry later. The time to retry is

- dependent on the implementation see clause 5.8 for more information.

- 416 NACK of an I3C Target address may indicate that the device buffers are full or the physical absence of

- 417 the device. The I3C Controller may test for the presence of a device after a NACK with the GETSTATUS

- 418 CCC. The I3C Target shall always respond to GETSTATUS CCC, even if its MCTP data buffer is full. The

- 419 I3C Controller shall retry GETSTATUS CCC as per Specification for I3C Basic<sup>SM</sup>, Improved Inter

- 420 <u>Integrated Circuit Basic</u>, clause 5.1.9.2.3 Retry Model for Direct GET CCC Commands, before it

- 421 considers the device as absent.

410

422

424

425

### 5.2.2 MCTP packet encapsulation: I3C Target to I3C Controller

- 423 Transmission of MCTP packets from I3C Target to I3C Controller can happen in two modes:

- In-Band Interrupt mode (IBI mode) or

- polling mode (described in clause 5.2.2.4).

The I3C Target is required to support both modes of operation and the I3C Controller can enable or disable IBIs as defined in *Specification for I3C Basic<sup>SM</sup>*, *Improved Inter Integrated Circuit – Basic*.

### 5.2.2.1 Overview – IBI mode

428

429

430

431

432

433434

435

437

438

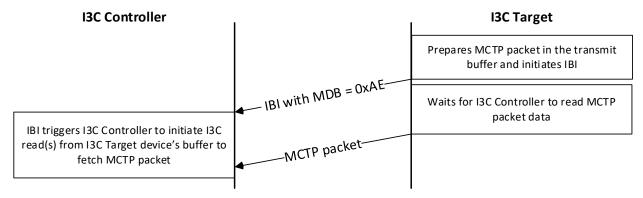

Transmission of MCTP packets from I3C Target to I3C Controller according to the IBI mode shall happen using the following general sequence:

- 1. When the I3C Target has a MCTP packet ready for transmission to the I3C Controller, it shall initiate an I3C IBI with MDB = 0xAE (as assigned in <u>MIPI Mandatory Data Byte (MDB) Values Table</u> registry) to inform the I3C Controller about the data ready.

- 2. The I3C Controller shall read the MCTP packet (or multiple packets) from the I3C Target using *I3C Private Read transfer*.

- 436 This sequence is illustrated in Figure 5:

Figure 5 - MCTP over I3C packet transfer sequence: I3C Target to I3C Controller

18 Published Version 1.0.1

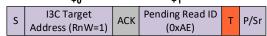

The transaction field explanations are illustrated in Figure 6 and in Table 2 (for pending read notification) and Table 3 (for the MCTP packet transfer):

440 441

442

443

444

445

446 447

448

449 450

451

452

453

454

455 456

457

439

### (1) Pending read notification using IBI (I3C Target to I3C Controller)

### (2) Actual MCTP packet transfer (I3C Controller to I3C Target)

Figure 6 - MCTP over I3C packet transfer format: I3C Target to I3C Controller

As defined in the <u>Specification for I3C Basic M, Improved Inter Integrated Circuit – Basic</u>, the read transfer may start with:

- (a) Repeated Start condition and the I3C Source (I3C Target) address immediately after the IBI or other traffic for example, using HCl auto-command as defined in <u>MIPI I3C<sup>SM</sup> Host Controller</u>

Interface<sup>SM</sup> Specification

- (b) Start condition and the I3C Target address

- (c) Start condition with I3C Broadcast Address (7'h7E), then Repeated Start with the I3C Target address

In these transactions, the T-bit is zero to indicate the End-of-Data – see <u>Specification for I3C Basic SM</u>, <u>Improved Inter Integrated Circuit – Basic</u>, clause 5.1.2.3.4 Ninth Bit of SDR Slave Returned (Read) Data as End-of-Data.

As per the <u>Management Component Transport Protocol (MCTP) Base Specification</u>, IC and Message Type byte is only present in the first packet of a fragmented MCTP message.

| Table 2 – IBI pending read notification field descriptions   |

|--------------------------------------------------------------|

| - a.b.o = - i=1 pointaing route inotation inotation and only |

| Byte | I3C Field(s)          | Description                                                                                   |

|------|-----------------------|-----------------------------------------------------------------------------------------------|

| 0    | I3C Target<br>Address | [7:1] I3C Target Address: The address of the I3C device that is the source of the MCTP packet |

|      | RnW                   | [0]: I3C RnW# bit: Shall be set to 1b for all IBIs                                            |

| Byte | I3C Field(s)                 | Description                                                                                                                           |

|------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Mandatory Data<br>Byte (MDB) | [7:0] 0xAE value – MCTP Pending Read ID notification as defined in <u>MIPI</u> <u>Mandatory Data Byte (MDB) Values Table</u> registry |

459

### Table 3 – MCTP packet transfer field descriptions

| Byte                                                                                             | I3C Field(s)          | Description                                                                                                                                                                                             |  |

|--------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0                                                                                                | I3C Target<br>Address | [7:1] I3C Target Address: The address of the I3C device that is the source of the MCTP packet                                                                                                           |  |

|                                                                                                  | RnW                   | [0]: I3C RnW# bit: Shall be set to 1b for all read transfers.                                                                                                                                           |  |

| 1                                                                                                | Read Data 1           | [7:4] MCTP reserved: This nibble is reserved for definition by the<br><u>Management Component Transport Protocol (MCTP) Base</u><br><u>Specification</u> .                                              |  |

|                                                                                                  |                       | [3:0] MCTP header version:                                                                                                                                                                              |  |

|                                                                                                  |                       | Set to 0001b for MCTP v1 devices that are conformant to the<br><u>Management Component Transport Protocol (MCTP) Base</u><br><u>Specification</u> and this version of the MCTP transport binding.       |  |

|                                                                                                  |                       | All other values = Reserved.                                                                                                                                                                            |  |

| 2                                                                                                | Read Data 2           | Destination Endpoint ID (*) as defined in <u>Management Component</u> <u>Transport Protocol (MCTP) Base Specification</u> , including special endpoint IDs                                              |  |

| 3                                                                                                | Read Data 3           | Source Endpoint ID (*) as defined in <u>Management Component Transport Protocol (MCTP) Base Specification</u> , including special endpoint IDs                                                          |  |

| 4                                                                                                | Read Data 4           | [7] SOM: Start Of Message flag (*)                                                                                                                                                                      |  |

|                                                                                                  |                       | [6] EOM: End Of Message flag (*)                                                                                                                                                                        |  |

|                                                                                                  |                       | [5:4] MCTP Packet sequence number (*)                                                                                                                                                                   |  |

|                                                                                                  |                       | [3] Tag Owner (TO) bit (*)                                                                                                                                                                              |  |

|                                                                                                  |                       | [2:0] Message tag (*)                                                                                                                                                                                   |  |

| 5                                                                                                | Read Data 5           | [7] IC: Integrity Check bit (*)                                                                                                                                                                         |  |

|                                                                                                  |                       | [6:0] Message type (*)                                                                                                                                                                                  |  |

| 6:N-1                                                                                            | Read Data 6:N-1       | MCTP message header and data (*)                                                                                                                                                                        |  |

| N                                                                                                | PEC                   | Packet error code (PEC): All MCTP I3C transfers shall include a PEC byte. The PEC byte shall be transmitted by the source and checked by the destination. Please see clause 5.3.1 for more information. |  |

| (*) Indicates a field that is defined by the Management Component Transport Protocol (MCTP) Base |                       |                                                                                                                                                                                                         |  |

(\*) Indicates a field that is defined by the <u>Management Component Transport Protocol (MCTP) Base Specification</u>.

460

461

462

463

464

465 466

### 5.2.2.2 Detailed flow

When a I3C Target has an MCTP packet available to transfer, it initiates the flow by sending an IBI with a Mandatory Data Byte (MDB) value = 0xAE. This is to inform the I3C Controller that an MCTP packet is available for reading from the I3C Target. The I3C Controller should acknowledge the IBI request and read the MDB data from the I3C Target. After accepting the request, the I3C Controller may read the packet immediately with a Repeated Start after the IBI or it may delay the read up to PT timeout – see

#### **DSP0233**

- 467 clause 5.8. The I3C Controller may queue up several IBI notifications from multiple I3C Targets and

- 468 process them in any order. Delaying reads allows prioritization as well as management of shared buffers

- but delays may result in IBI retransmissions see clause 5.2.2.3.

- When sending the IBI notification, the I3C Target needs to ensure that the MDB has been read by the I3C

- 471 Controller and ensure the data is available for the next private read request from the I3C Controller. If the

- 472 I3C Controller NACKs the IBI, then the IBI was not accepted and the I3C Target shall retry the IBI at the

- next opportunity as per <u>Specification for I3C Basic SM</u>, <u>Improved Inter Integrated Circuit Basic</u>, section

- 474 5.1.6.2, Slave Interrupt Request and conformant to section 5.8. The I3C Target may interpret consecutive

- NACKs of an IBI as an error and take actions dependent on implementation.

- 476 Once the I3C Target has sent all the bytes of the MCTP packet and the PEC byte, the I3C Target shall

- 477 indicate the end of data transfer, and the I3C Controller completes the I3C transaction. The next MCTP

- 478 packet transfer shall happen in a separate transfer. The error cases for this rule are described in clause

- 479 5.2.2.7.

480

499

510 511

#### 5.2.2.3 ACKed IBI retransmissions

- 481 Each I3C Target shall also implement a timeout mechanism in order to retransmit the IBI. The timer shall

- 482 be started when the I3C Controller acknowledges the IBI with MDB. The I3C Target shall retransmit the

- 483 IBI if the read has not happened within a certain time. The number of retransmits and the timeout value

- are implementation dependent depends on the I3C Target functionality, I3C Controller capabilities, and

- characteristics of MCTP traffic (urgency of retransmission) and shall conform to clause 5.8 requirements.

- The I3C Target shall also wait for at least one Tidle condition on the bus between retransmits.

### 487 **5.2.2.4 Polling mode**

- The I3C Controller can operate in polling mode when IBIs are disabled. In this case, the I3C Controller

- 489 can do a GETSTATUS CCC to find if IBIs are pending (pending read notifications are reported as a

- 490 pending IBI) or it may simply attempt read transfers from the I3C Target and see if it responds with data.

- When responding to GETSTATUS CCC, MCTP I3C Targets shall report a non-zero value in the pending

- 492 interrupt field to indicate that at least one MCTP packet is ready to be read. The convention is that the

- 493 pending interrupt value 1 is the least important priority and 15 is the most important priority. Unless

- overridden by a different specification or protocol, the default value should be 7. The I3C Controller is

- expected to read from the I3C Target if a non-zero pending interrupt value is reported. It may use the

- 496 value as a relative priority hint.

- 497 To avoid MCTP packet loss, the I3C Controller shall read the pending packet according to the MCTP

- 498 timeouts defined in clause 5.8.

#### 5.2.2.5 Sequences of multiple MCTP packets and reads without IBIs

- 500 If the I3C Target has multiple MCTP packets to send to the I3C Controller, it may signal multiple IBIs, one

- for each packet. This may happen even if waiting for the I3C Controller to initiate a private read request

- on a prior MCTP packet. An I3C Target may only signal multiple ready packets if it is able to service

- 503 sequential I3C Controller reads separated by a Repeated Start. I3C Targets that are unable to respond

- 504 quickly enough to a sequence of reads separated by Repeated Start conditions shall delay IBI

- notifications of additional packets until after the prior packet is read.

- The I3C Controller may also do multiple MCTP packets reads in a sequence even without having received multiple IBIs, as in the following examples:

- If the I3C Controller receives a multi-packet MCTP message, it may attempt to read subsequent MCTP packets until EOM flag is set in the MCTP header,

- The I3C Controller knows that the I3C Target transmits MCTP packets on strictly periodical basis.

- The I3C Controller expects more MCTP packets, so it decides to continue reading until a NACK is received (see clause 5.2.2.6 for more information).

- In the above scenarios, the I3C Target shall not send IBIs related to packets that have been read by the

- 515 I3C Controller.

- 516 If IBIs are disabled, the I3C Target shall still respond to private reads and provide the next available

- 517 MCTP packets.

529

539

- 518 **5.2.2.6 NACKs**

- 519 If the I3C Controller attempts a read when the I3C Target has no MCTP packets ready to send, then the

- 520 I3C Target shall NACK the address byte.

- The I3C Controller shall follow the flow discussed in clause 5.2.1.2 to differentiate between an I3C Target

- device no longer present and an I3C Target device NACKing the transfers.

- 523 **5.2.2.7 Early terminated or prolonged reads**

- The I3C Target expects the whole MCTP packet to be read by the I3C Controller. It may happen,

- 525 however, that the I3C Controller terminates the read transfer too early or too late:

- The I3C Controller stops before the I3C Target transmits the whole MCTP packet, including the PEC byte, due to unexpected packet content, packet length limit mismatch, or bus errors.

- The I3C Controller continues to drive the clock even after the I3C Target indicated the end of transaction due to bit error on T-bit or clock synchronization error.

- If this happens, the I3C Controller should interpret the last byte of the received data as PEC to detect

- 531 packet data corruption and discard the packet. The I3C Target shall infer that the I3C Controller received

- 532 corrupted MCTP packet and retransmit it again from the beginning on the next private read. If IBIs are

- enabled, the I3C Target shall use an IBI to notify the I3C Controller that it has a packet waiting just as if it

- had a new packet for transmission.

- 535 **5.2.2.8 Future performance enhancements**

- IBI speeds are limited to I3C SDR mode only, so the amount of data transferred in the IBI was minimized

- 537 and instead transferred on a subsequent private read. This enables future migration of reads to I3C HDR

- mode for more efficient transfer of potentially larger MCTP packets.

- 5.3 Error detection and handling mechanisms

- 540 5.3.1 MCTP data packets

- 541 MCTP relies on the underlying transport to provide packet-level error detection. For I3C, the PEC byte is

- 542 used to detect transmission errors as described in clause 5.2. The polynomial for CRC-8 calculation is as

- follows same as SMBus PEC and the initial value and a final XOR values are zeros:

- $C(x) = x^8 + x^2 + x^1 + 1$

- The PEC is calculated independently for each MCTP packet using the same method as for SMBus PEC,

- 546 as defined in <u>System Management Bus (SMBus) Specification</u>. It is calculated over the I3C

- source/destination address field, RnW# bit, and all MCTP packet bytes of an I3C private read or write

- 548 transfer (not for CCCs, IBIs, or other preamble traffic). The PEC is inserted at the end of each MCTP

- 549 packet prior to its termination with Stop or Repeated Start condition see Figure 4 and Figure 6. The

- 550 PEC calculation excludes Start, Repeated Start, Stop, 7'h7E broadcast address, T-bits, ACK, and NACK.

#### **DSP0233**

555

556

557

558

559

560

561

562

565

566

567 568

569

570

571

573

- The receiver of the MCTP packet shall verify if the PEC byte is correct for the packet content. If it detects an error, it should discard the received packet.

- 553 When the sender detects the transmission error, it is recommended to retransmit the corrupted packet.

554 These scenarios are:

- In case of Target-to-Controller transfer, if the transfer is terminated too early or too late, the I3C Target can retransmit the packet see clause 5.2.2.7 for more information,

- If the I3C Target detects error type S6 or the I3C Controller detects error type M1, then it terminates the data transfer early, as defined in <u>Specification for I3C Basic M, Improved InterIntegrated Circuit Basic.</u> In this case, the MCTP packet can be retransmitted.

- In the above case, thanks to the last byte interpreted as PEC by the receiver, the error is expected to be detected and the corrupted packet data discarded.

### 5.3.2 CCC error detection and handling

The following recommendations should be followed in order to lower the probability of silent errors during I3C CCCs:

- The dynamic addresses should be assigned for maximum Hamming distance between any two

addresses without using reserved addresses listed in <u>Specification for I3C Basic<sup>SM</sup>, Improved</u>

<u>Inter Integrated Circuit Basic</u> this is to lower the probability of an incorrect device receiving a

CCC.

- CCCs should be individually terminated with a Stop condition this is to prevent getting stuck in Dynamic Address Assignment mode,

- Table 4 recommends the best workarounds to make mandatory CCCs more reliable.

- 572 Enhancements for optional CCCs are implementation dependent.

### Table 4 – Recommended behaviors for robust CCCs

| ccc       | Error Description                                                                                                                                                                                 | Recommended Behavior                                                                                                                                                                                                                                             |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GETBCR    | Incorrect value read (due                                                                                                                                                                         | Keep issuing CCC until 2 consecutive read values match.                                                                                                                                                                                                          |

| GETDCR    | to bit errors in the data<br>field) or value from wrong<br>device (due to bit errors<br>in the address field)                                                                                     | Discard any reads returning invalid values.                                                                                                                                                                                                                      |

| GETMRL    |                                                                                                                                                                                                   | For GETSTATUS, if the difference between the first and second reading is only the auto cleared Protocol Error flag they should                                                                                                                                   |

| GETMWL    |                                                                                                                                                                                                   | be considered as a match with the Protocol Error flag set.                                                                                                                                                                                                       |

| GETPID    |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                  |

| GETSTATUS |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                  |

| ENEC      | Incorrect enable/disable                                                                                                                                                                          | An unexpected IBI received from a device indicates a redundant                                                                                                                                                                                                   |

| DISEC     | event byte value or<br>wrong address (includes<br>S1, S2 error types<br>defined in <u>Specification</u><br>for I3C Basic <sup>SM</sup> .<br>Improved Inter Integrated<br><u>Circuit – Basic</u> ) | DISEC IBI command is required.                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                   | If an I3C Controller times out when waiting for an IBI from an I3C Target, then it is possible that the I3C Target interrrupts are unintentionally disabled and the I3C Controller should use GETSTATUS to see if an interrupt is pending and enable IBIs again. |

| ccc                                                                                                                                                                                                                         | Error Description                                                                                                                                                                                                                       | Recommended Behavior                                                                                                                                                                                                                                                                         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ENTDAA                                                                                                                                                                                                                      | Incorrect CCC received (S1 error defined in Specification for I3C Basic M. Improved Inter Integrated Circuit – Basic or undetected by parity check) or wrong address (due to bit errors in the address field)                           | Assign addresses to all participating devices that do not yet have a dynamic address then repeat CCC until two consectutive ENTDAAs do not detect additional devices. Confirm address assignments with ACK from directed traffic to that address.                                            |  |  |  |

| SETNEWDA  If a new address is set incorrectly, wrong device changes address, two devices may end up with same address (S2 error type defined in Specification for I3C  Basic SM, Improved Inter Integrated Circuit — Basic) |                                                                                                                                                                                                                                         | I3C Controller shall issue a GETPID CCC before and after SETNEWDA to verify if the same device responds at the new address.  If there is an error (device does not respond or a different PID is detected), recovery would be via reasssigning all dynamic addresses on the bus with RSTDAA. |  |  |  |

| ENTAS0                                                                                                                                                                                                                      | CCC not recognized by I3C Target (S1 error defined in <u>Specification for I3C Basic SM</u> , <u>Improved Inter Integrated Circuit – Basic</u> or undetected by parity check) or wrong address (due to bit errors in the address field) | AS-type CCCs are just hints so errors can be ignored.                                                                                                                                                                                                                                        |  |  |  |